数控分频器设计(数控分频器设计EDA实验报告)

- 设计

- 2024-02-22 15:40:16

- 63

用VHDL设计一个数控分频器电路,要求三分频,占空比50%。

1、最后分出假设就是10Msignal clk10MHZ :std_logic; beginprocess(clk,rst)variable cnt:integer:=0;if rst=0 then 清零,这个应该会写吧elsif clk上升沿来临 then (用rising_edge(clk)简单代码短点儿。。

2、分频(触发器)的实现 输入端为:时钟信号clk,输入信号d;输出端为:q:输出信号a,q1:输出信号a反。其VHDL语言略。

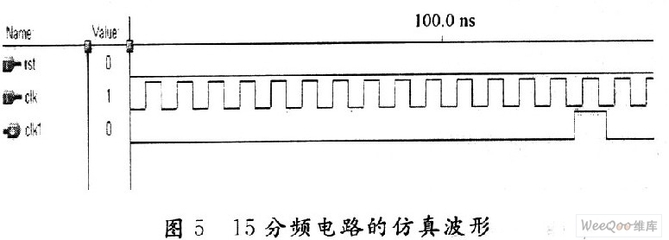

3、以下是,核心板的时钟是50MHz,通过sel[1:0]选择分频数,00:不分频;01:15M分频;10:25M四分频;11:50M分频。采用SW1‐SW2设置分频值,SW3复位。LED1为时钟的输出,通过调整SWSW2,可以得到不同的闪烁频率。

音箱分频器电路图册

要推动这两个喇叭,还需要用分频器带动,才能发挥出它的威力。使低音效果更加震撼有力、高音效果更加清脆、悦耳透明,发出银铃般的声音。这样音箱所发出来的高低音才能得到互补、悦耳动听。

音箱分频器是一种组合式滤波器,可以将声音信号分成若干个频段。音响的二路分频器就是由一个高通滤波器和一个低通滤波器组成,而三路分频则又增加了一个带通滤波器。

使用分频器带动喇叭,功放机输出功率最小在10瓦以上、低音喇叭口径也应该在七寸以上才行。两分频器电路图如下:图中的L可以用0.5~0.8的漆包线绕成空心线圈150~200圈。

怎么设计74LS195分频器?

把同一片74LS74上的两路D触发器串联起来,其中一个D触发器的输出作为另一个D触发器的时钟信号,就可以实现四分频。

首先找到一块74LS195芯片,将其J、K输入端连接到一起,将R、LOAD端连接高电平,将CP端连接脉冲信号,再将输出端从左到右、从上到下编号为Q0、QQQ3,如图所示。

利用194来设计奇数或偶数型的计数器,可以用反馈移位的方法来设计,具体可以见西安电子科技大学出版社,杨颂华编的数字电子技术基础,第七章关于74LS194的部分 。设计时请注意能否自启动的问题。

本文由admin于2024-02-22发表在贵州在线,如有疑问,请联系我们。

本文链接:https://www.gz162.com/post/147663.html

![安卓手机强制恢复出厂(安卓手机强制恢复出厂设计)[20240426更新]](http://www.gz162.com/zb_users/upload/editor/20230114/63c1b2835d31e.jpg)

![机箱风道设计(机箱风道设计原则)[20240424更新]](http://www.gz162.com/zb_users/upload/editor/20230114/63c1a4f773c8a.jpg)

![打印机维修(打印机维修报告怎么写)[20240420更新]](http://www.gz162.com/zb_users/upload/editor/20230114/63c18a341deeb.jpg)

![低音炮音箱(低音炮音箱设计原理图)[20240420更新]](http://www.gz162.com/zb_users/upload/editor/20230114/63c188487ee48.jpg)

![家庭影院设计(家庭影院设计效果图)[20240419更新]](http://www.gz162.com/zb_users/upload/editor/20230114/63c182eb110fc.jpg)

![联想zukz2(联想ZuKz2)[20240419更新] 联想zukz2(联想ZuKz2)[20240419更新]](https://www.gz162.com/zb_users/upload/editor/20230114/63c1814419d63.jpg)

![1000左右买什么平板电脑最好的简单介绍[20240419更新] 1000左右买什么平板电脑最好的简单介绍[20240419更新]](https://www.gz162.com/zb_users/upload/editor/20230114/63c18151a11b1.jpg)

![组装机电脑配置清单2021(组装机电脑配置清单2021款)[20240419更新] 组装机电脑配置清单2021(组装机电脑配置清单2021款)[20240419更新]](https://www.gz162.com/zb_users/upload/editor/20230114/63c1812cb194e.jpg)