减法电路设计(减法电路设计的计算公式)

- 设计

- 2024-02-29 07:35:21

- 63

数字逻辑电路,求电路图!!用74LS192设计6进制减法计数器,外部反馈置数法...

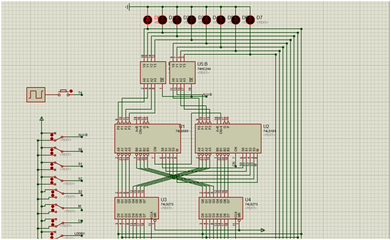

一)首先要使用74LS192或40192设计一个4进制计数器和一个7进制计数器,然后通过数码管来显示状态。两种进制间的切换可以通过一个单刀双掷开关来实现。其重点和难点在于设计一个4进制计数器和一个7进制计数器。

LS192加/减计数器各用时钟信号,手动控制就用一个单刀双掷开关选择加/减时钟信号就行了。下面是仿真图,数码管是用来显示仿真效果的,你可以不用画。加法计数状态,K1选择加法时钟信号端UP。减法计数状态。请及时采纳。

LS161是一个同步的可预置的四位二进制计数器,并自带有异步功能。可以采用反馈归零法进行6进制的计数器设计。

试用单一运算放大器,设计一个减法电路,输入为电压V1和V2,输出为V3=V2...

1、实用电路如下图,其中R1=R2,R3=R4,R5=R6。如果V3的范围是-6V~+6V,运放的工作电源电压设置为±9V为宜,这是考虑到运放可能不是满电源幅度输出的型号。

2、设计电路如下图所示:其实就是一个差分放大器,放大倍数为0.5(10k/20k),其中电阻阻值可以修改,但是比例不能改。

3、-11-16 用集成运算放大器设计一电路,实现vo=3vi1-2vi2 (... 7 2018-02-05 电路如图所示,已知R1=R2=R3=R4,假设运放是理想的。... 2018-07-20 ,试求电路输出电压vo与输入电压vIvI2的运算关系式。

4、电路叠加原理,V1,V2在正端,V3在负,然后配电组。

四位二进制减法计数器电路图

基本构成:该计数器通常由几个基本的电子器件组成,如门电路、触发器、加法器等。逻辑设计:二进制减法涉及减数、被减数和结果的计算。常用的是采用加法器对减数进行取反(求补码),然后将被减数与补码相加。

【答案】:用4位二进制并行加法器设计一个4位二进制并行加法/减法器. 解 设A和B分别为4位二进制数,其中A=a4a3a2a1为被加数(或被减数),B=b4b3b2b1为加数(或减数),S=s4s3s2s1为和数(或差数)。

要改成减法计数器,可将4个输出端各接一个非门,则原输出的状态取反后变成1111~0000,即F~0,就是减法计数了,逻辑图如下,也是仿真图。计数输出为0000,经4个非门取反后成为1111,十六进制数的F。

一下内容是两个问题的具体解由于只能传一个图片,所以我把仿真结果的四个图都放在了最后的图里面,用时自己保存下来后在截图吧。第1题:考试题目任意题目设计:设计一个4位二进制减法计数器,并含有异步清零信号。

是四位二进制加/减计数器,两片级联就可以组成8位二进制加/减计数,就是256进制。逻辑图如下所示,也是仿真图,数码管只是用来显示仿真效果的,你可以不用画。这是加法到最大数255时的截图。

vhdl 四位二进制同步减法计数器(异步清零、同步预置、下降沿触发、带借位输出BO端)的实现,该程序已经仿真通过,产生的波形图如图所示。

设计一个减法运算电路,使输出为V0=V1-V2

1、其实就是一个差分放大器,放大倍数为0.5(10k/20k),其中电阻阻值可以修改,但是比例不能改。

2、实现和第一个运放输出的减法运算。先看第二个运放的输出:(V01-Vn)/R2+(V2-Vn)/(R2/2)=(Vn-V0)/R2,且Vn=0。所以:V01+2V2=-V0,即:V0=-V01-2V2。

3、用运放构成减法器电路,减法器的放大倍数设置为10倍。

减法电路原理是什么

1、总之,减法运算电路实验原理是将减法转化成加法,并利用二进制加法器和控制电路实现减法运算,进而得出结果.另外,在实际应用中,减法运算可以通过电路设计中经典的差分器实现。差分器由两个异或门和一个与门组成。

2、减法器电路与原理减法器是一种电路,它可以实现二进制数字的减法运算。减法器的工作原理基于位运算和进位/借位机制。常见的减法器有硬件实现的二进制减法器和软件实现的程序减法器。

3、而加减运算电路则是基于运算放大器的反相输入端和正相输入端的电势差来实现的,其原理是将两个信号的加减操作转化为电压的加减操作,来实现四则运算。

4、运算功能:加法运算电路用于执行数字加法操作,将两个或多个输入信号相加并输出其和。它可以执行二进制的逐位相加运算。而减法运算电路用于执行数字减法操作,将两个输入信号相减并输出差值。

设计一个加减运算电路

1、设计电路如下图。同相端:Vp=Vi1×R/(R+R)=0.5Vi1。虚短:Vp=Vn=0.5Vi1。虚断:(Vi2-Vn)/R=(Vn-Vo)/R,于是:Vo=2Vn-Vi2=Vi1-Vi2。

2、【答案】:用4位二进制并行加法器设计一个4位二进制并行加法/减法器. 解 设A和B分别为4位二进制数,其中A=a4a3a2a1为被加数(或被减数),B=b4b3b2b1为加数(或减数),S=s4s3s2s1为和数(或差数)。

3、y=(1+k)(A1x1+A2x2+A3x3)=(1+12)×(2x1+4x2+10x3)/12= 2x1+4x2+10x3。参数选择结果:r1=10kΩ,r2=3kΩ,r3=2kΩ,rf=12kΩ,r=1kΩ。

4、”;根据“虚短”,反相输入端电位也为“0”。对于第一个集成运放:(x1-0)/R+(x2-0)/0.5R=(0-Y1)/R。Y1=-(x1+2x2)。第二个集成运放:(Y1-0)/r=(0-Y)/r,Y=-Y1。所以:Y=x1+2x2。

5、分析与方案选择(一)首先要使用74LS192或40192设计一个4进制计数器和一个7进制计数器,然后通过数码管来显示状态。两种进制间的切换可以通过一个单刀双掷开关来实现。

6、总之,减法运算电路实验原理是将减法转化成加法,并利用二进制加法器和控制电路实现减法运算,进而得出结果.另外,在实际应用中,减法运算可以通过电路设计中经典的差分器实现。差分器由两个异或门和一个与门组成。

本文由admin于2024-02-29发表在贵州在线,如有疑问,请联系我们。

本文链接:https://www.gz162.com/post/149468.html

![电脑配置表2021(电脑配置表全自动计算)[20240424更新]](http://www.gz162.com/zb_users/upload/editor/20230114/63c1a031f0429.jpg)

![联想zukz2(联想ZuKz2)[20240419更新] 联想zukz2(联想ZuKz2)[20240419更新]](https://www.gz162.com/zb_users/upload/editor/20230114/63c1814419d63.jpg)

![1000左右买什么平板电脑最好的简单介绍[20240419更新] 1000左右买什么平板电脑最好的简单介绍[20240419更新]](https://www.gz162.com/zb_users/upload/editor/20230114/63c18151a11b1.jpg)

![组装机电脑配置清单2021(组装机电脑配置清单2021款)[20240419更新] 组装机电脑配置清单2021(组装机电脑配置清单2021款)[20240419更新]](https://www.gz162.com/zb_users/upload/editor/20230114/63c1812cb194e.jpg)